- 您现在的位置:买卖IC网 > Sheet目录1971 > UPD78F1168AGF-GAS-AX (Renesas Electronics America)MCU 16BIT 78K0R/KX3 100-LQFP

CHAPTER 3 CPU ARCHITECTURE

User’s Manual U17894EJ9V0UD

98

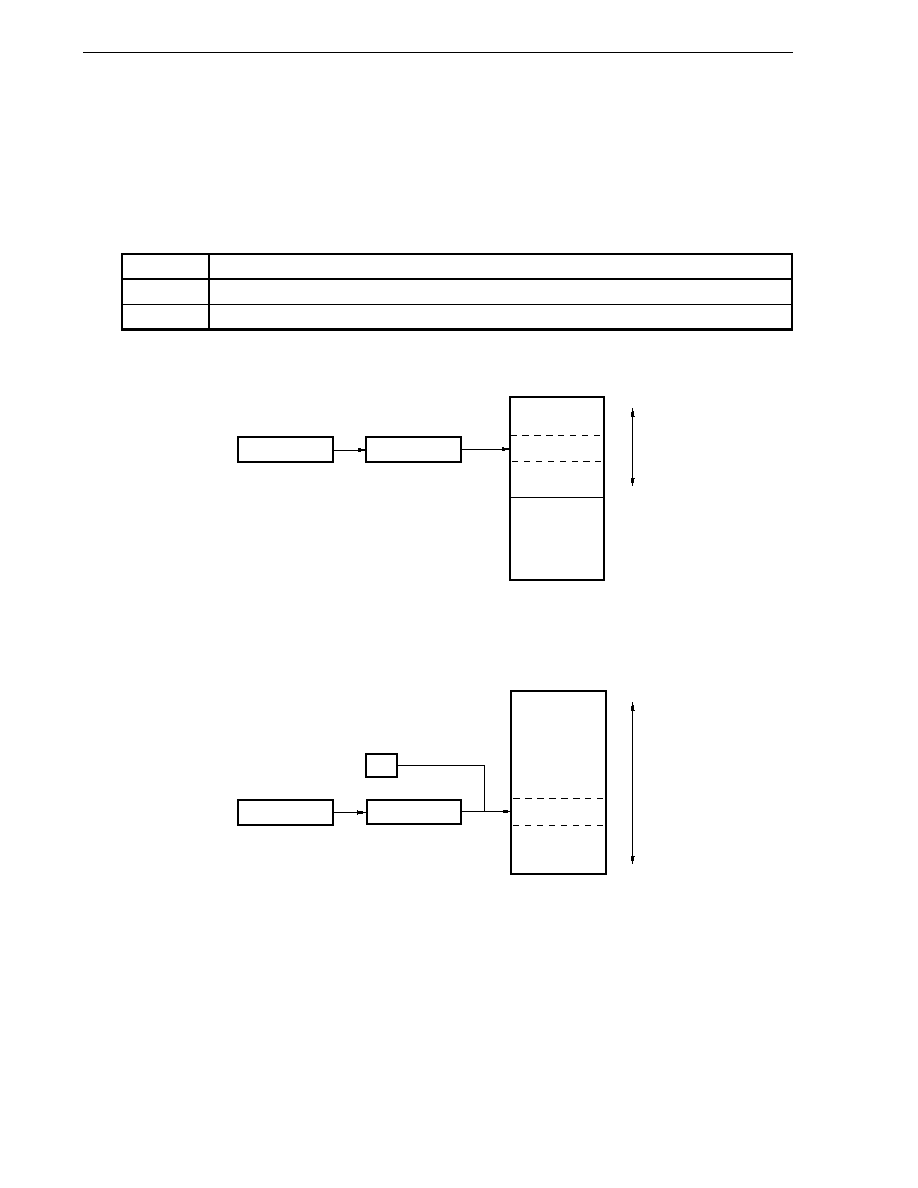

3.4.6 Register indirect addressing

[Function]

Register indirect addressing directly specifies the target addresses using the contents of the register pair

specified with the instruction word as an operand address.

[Operand format]

Identifier

Description

[DE], [HL] (only the space from F0000H to FFFFFH is specifiable)

ES:[DE], ES:[HL] (higher 4-bit addresses are specified by the ES register)

Figure 3-33. Example of [DE], [HL]

Target memory

OP code

Memory

rp

FFFFFH

F0000H

Figure 3-34. Example of ES:[DE], ES:[HL]

OP code

Memory

FFFFFH

00000H

Target memory

ES

rp

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

UPD78F1178AGF-GAT-AX

MCU 16BIT 78K0R/KX3 128-LQFP

UPD78F1188AGJ-GAE-AX

MCU 16BIT 78K0R/KX3 144-LQFP

UPD78F1235GK-GAJ-AX

MCU 16BIT 78K0R/LX3 64-LQFP

UPD78F4225YGC-8BT-A

MCU 16BIT 128K FLASH

UPD78F9202MA-CAC-A

MCU 8BIT 4KB FLASH 128B RAM

UPD78F9212CS-CAB-A

MCU 8BIT 4KB FLASH 16PIN

UPD78F9222CS-CAC-A

MCU 8BIT 4KB FLASH 20PIN

UPD78F9234CS-CAA-A

MCU 8BIT 8KB FLASH 30PIN

相关代理商/技术参数

UPD78F1168GC-UEU-AX

制造商:Renesas Electronics Corporation 功能描述:

UPD78F1168GF-GAS-AX

制造商:Renesas Electronics Corporation 功能描述:

UPD78F1174AGF-GAT-AX

功能描述:MCU 16BIT 78K0R/KX3 128-LQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:78K0R/Kx3 标准包装:250 系列:80C 核心处理器:8051 芯体尺寸:8-位 速度:16MHz 连通性:EBI/EMI,I²C,UART/USART 外围设备:POR,PWM,WDT 输入/输出数:40 程序存储器容量:- 程序存储器类型:ROMless EEPROM 大小:- RAM 容量:256 x 8 电压 - 电源 (Vcc/Vdd):4.5 V ~ 5.5 V 数据转换器:A/D 8x10b 振荡器型:内部 工作温度:-40°C ~ 85°C 封装/外壳:68-LCC(J 形引线) 包装:带卷 (TR)

UPD78F1174GF-GAT-AX

制造商:Renesas Electronics Corporation 功能描述:

UPD78F1175AGF-GAT-AX

功能描述:MCU 16BIT 78K0R/KX3 128-LQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:78K0R/Kx3 标准包装:250 系列:80C 核心处理器:8051 芯体尺寸:8-位 速度:16MHz 连通性:EBI/EMI,I²C,UART/USART 外围设备:POR,PWM,WDT 输入/输出数:40 程序存储器容量:- 程序存储器类型:ROMless EEPROM 大小:- RAM 容量:256 x 8 电压 - 电源 (Vcc/Vdd):4.5 V ~ 5.5 V 数据转换器:A/D 8x10b 振荡器型:内部 工作温度:-40°C ~ 85°C 封装/外壳:68-LCC(J 形引线) 包装:带卷 (TR)

UPD78F1176AGF-GAT-AX

功能描述:MCU 16BIT 78K0R/KX3 128-LQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:78K0R/Kx3 标准包装:250 系列:80C 核心处理器:8051 芯体尺寸:8-位 速度:16MHz 连通性:EBI/EMI,I²C,UART/USART 外围设备:POR,PWM,WDT 输入/输出数:40 程序存储器容量:- 程序存储器类型:ROMless EEPROM 大小:- RAM 容量:256 x 8 电压 - 电源 (Vcc/Vdd):4.5 V ~ 5.5 V 数据转换器:A/D 8x10b 振荡器型:内部 工作温度:-40°C ~ 85°C 封装/外壳:68-LCC(J 形引线) 包装:带卷 (TR)

UPD78F1177AGF-GAT-AX

功能描述:MCU 16BIT 78K0R/KX3 128-LQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:78K0R/Kx3 标准包装:250 系列:80C 核心处理器:8051 芯体尺寸:8-位 速度:16MHz 连通性:EBI/EMI,I²C,UART/USART 外围设备:POR,PWM,WDT 输入/输出数:40 程序存储器容量:- 程序存储器类型:ROMless EEPROM 大小:- RAM 容量:256 x 8 电压 - 电源 (Vcc/Vdd):4.5 V ~ 5.5 V 数据转换器:A/D 8x10b 振荡器型:内部 工作温度:-40°C ~ 85°C 封装/外壳:68-LCC(J 形引线) 包装:带卷 (TR)

UPD78F1177AGF-GAT-E2-AX

制造商:Renesas Electronics Corporation 功能描述: